Микросхемы для "ЮТ-88"

- КР580ГФ24 - микросхема генератора тактовых сигналов

- KP580BК38 - микросхема системного контроллера и буферного регистра данных

- КР580ИР82 - микросхема 8-разрядного адресного регистра

- КР580ВВ55А - программируемое устройство ввода/вывода параллельной информации

- К589ИР12 - многорежимный восьмиразрядный универсальный буферный регистр

- К589АП16 и К589АП26 - двунаправленные шинные формирователи

КР580ГФ24 - микросхема генератора тактовых сигналов, используемого для синхронизации работы микропроцессора KP580BM80A.

Генератор формирует две фазы С1 и С2 с импульсами положительной полярности, амплитудой 12 В и частотой 0,5 - 3,0 МГц. Кроме того, генератор выдает тактовые сигналы опорной частоты с амплитудой около 5 В (уровень микросхем ТТЛ), стробирующий сигнал состояния STB и тактовые сигналы С, синхронизированные с фазой С2 с амплитудой ТТЛ уровня.

Генератор синхронизирует сигналы RDYIN и RESLN фазой С2.

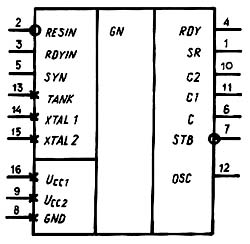

Условное графическое обозначение микросхемы и ее структурная схема показаны на рисунках 1 и 2. В таблице 1 приведены назначения ее выводов.

|

|

|

| Графическое обозначение м/сх КР580ГФ24 | Структурная схема м/сх КР580ГФ24 |

Таблица 1

|

Генератор тактовых сигналов состоит из генератора опорной частоты, счетчика-делителя на 9, формирователя фаз С1 и С2 и логических схем. Для стабилизации тактовых сигналов опорной частоты ко входам XTA1L1 и ХТА1L2 генератора подключается кварцевый резонатор, частота которого должна быть в 9 раз больше частоты выходных сигналов С1 и С2. В радиолюбительской практике чаще всего используются кварцевые резонаторы 15 - 20 МГц. Если частота кварцевого резонатора больше 10 МГц, то последовательно с ним необходимо включить конденсатор емкостью 3 - 10 пФ.

Выход TANK предназначен для подключения колебательного контура, работающего на высших гармониках резонатора.

Контур стабилизирует тактовые сигналы опорной частоты.

Тактовые сигналы, синхронные с сигналами опорной частоты, с выхода OSC используются в том случае, если в микропроцессорной системе установлены несколько генераторов и надо синхронизировать их работу.

Стробирующий сигнал состояния STB формируется при наличии на входе SYN напряжения высокого уровня, поступающего с выхода микропроцессора KP580ВM80A в начале каждого машинного цикла. Сигнал STB используют для занесения информации состояния микропроцессора в микросхему КР580ВК28 или КР580ВК38 для формирования ими управляющих сигналов.

Для согласования работы микропроцессора КР580ВМ80А с другими устройствами сигнал RDYIN синхронизируется по фазе С1 на выходе RDY генератора. Выходной сигнал SR используют для установки в исходное состояние микропроцессора и других микросхем в системе.

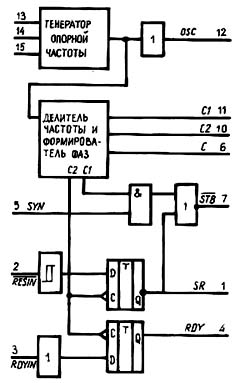

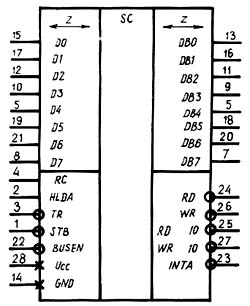

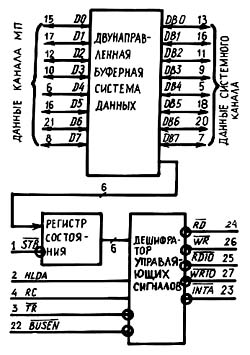

KP580BК38 (прежнее обозначение КР580ИК38) - микросхема системного контроллера и буферного регистра данных. Используется в компьютерах и микропроцессорных системах, собранных на базе микропроцессора KP580BM80A как формирователь управляющих сигналов и как буферный регистр данных. Условное графическое изображение микросхемы и ее структурная схема показаны на рисунках 3 и 4. Назначение выводов - в таблице 2.

|

|

|

| Графическое обозначение м/сх KP580BК38 | Структурная схема м/сх KP580BК38 |

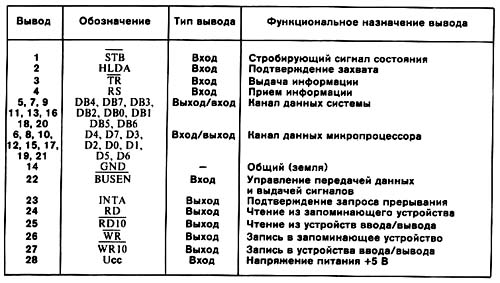

Таблица 2

|

Системный контроллер формирует управляющие сигналы по сигналам состояния микропроцессора при обращении: к запоминающим устройствам RD и WR, при обращении к устройствам ввода/вывода RD10 и WR10, INTA, а также обеспечивает прием и передачу 8-разрядной информации между каналами данных микропроцессора (выводы D7 - D0) и системным каналом по выводам DB7 - DB0.

Системный контроллер состоит из двунаправленной буферной схемы данных, регистра состояний и дешифратора управляющих сигналов.

Восьмиразрядная параллельная трехстабильная буферная схема данных принимает информацию с канала данных микропроцессора по выводам D7 - D0 и передает в регистр состояния информацию состояния, на системный канал по выводам DB7 - DB0 выдает данные в цикле записи по сигналу ТR. В цикле чтения по сигналу RC буферная схема принимает данные с системного канала по выводам DB7 - DB0 и передает их по выводам D7 - D0 на канал данных микропроцессора.

Регистр состояния по входному сигналу STB фиксирует информацию состояния микропроцессора в такте Т1 каждого машинного цикла микропроцессора.

Дешифратор управляющих сигналов формирует один из управляющих сигналов в каждом машинном цикле: при чтении ЗУ - RD, при записи в ЗУ - WR, при считывании информации из устройств ввода/вывода - RD10, при записи в них - WR10, при подтверждении запроса прерывании - сигнал INTA.

Асинхронный сигнал BUSEN управляет выдачей данных с буферной схемы и управляющих сигналов с дешифратора. При напряжении низкого уровня на входе BUSEN буферная схема передает все данные и формируется один из управляющих сигналов; при напряжении высокого уровня все выходы микросхемы переходят в высокоомное состояние.

Напряжение высокого уровня на входе HLDA переводит выходы RD, RD10 и INTA в пассивное состояние (высокого уровня) и блокирует передачу информации через буферную схему данных.

Управляющие сигналы WR и WR10 формируются в цикле записи по сигналу STB.

При работе с микропроцессором К580ВМ80А системный контроллер в цикле подтверждения запроса прерывания формирует три сигнала INTA для приема трех байтов команды CALL от контроллера прерывания (если он есть).

В небольших микропроцессорных системах выход INTA микросхем KP580BK38 можно подсоединять к напряжению + 12 В через резистор 1 кОм. Во время действия сигнала RC буферная шина данных микросхемы формирует код команды RST7 и передает его на канал данных микропроцессора.

Таким образом, микросхема - единственный вектор прерывания с номером 7 без дополнительных компонентов.

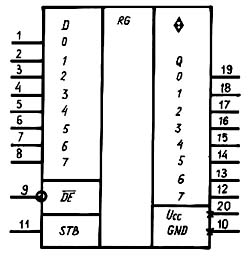

КР580ИР82 - микросхема 8-разрядного адресного регистра, предназначенная для связи микропроцессора с системной шиной; обладает повышенной нагрузочной способностью. Микросхема КР580ИР82 - восьмиразрядный D-регистр с "защелкой" без инверсии и с тремя состояниями на выходе. Условное графическое обозначение и ее структурная схема приведены на рисунках 5 и 6. Назначение выводов - в таблице 3.

|

|

|

| Графическое обозначение м/сх КР580ИР82 | Структурная схема м/сх КР580ИР82 |

Таблица 3

|

Микросхема состоит из восьми одинаковых функциональных блоков и схемы управления. Блок содержит D-триггер - "защелку" и мощный выходной вентиль. При помощи схемы управления производится стробирование записываемой информации и управление третьим состоянием мощных выходных вентилей.

В зависимости от состояния стробирующего сигнала STB микросхемы могут работать в двух режимах: в режиме шинного формирователя или в режиме хранения. При высоком уровне сигнала STB и низком сигнале ОЕ микросхема работает в режиме шинного формирователя: информация на выходах Q повторяется или инвертируется по отношению к входной информации D. При переходе сигнала STB из состояния высокого уровня в низкий происходит "защелкивание" передаваемой информации во внутреннем триггере, и она сохраняется до тех пор, пока на входе STВ присутствует напряжение низкого уровня. В течение этого времени информация на входах не влияет на состояние выходов Q. При переходе сигнала STB вновь в состояние высокого уровня состояние выходов приводится в состояние, соответствующее информационным входам Q.

При переходе сигнала ОЕ в состояние высокого уровня все выходы Q переходят в высокоомное состояние независимо от входных сигналов STB и Q. При возвращении сигнала ОЕ в состояние низкого уровня выходы Q переходят в состояние, соответствующее внутренним триггерам.

При обращении к внешнему устройству микропроцессор в начальный период цикла выполнения микрокоманды выдает на местную шину адрес этого устройства, который через системную шину передается необходимым числом регистров микросхемы.

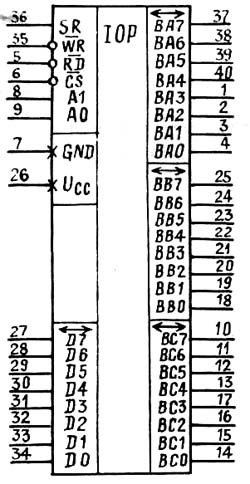

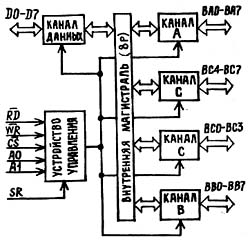

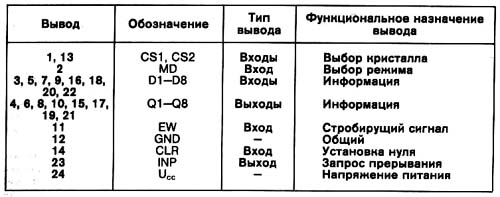

Микросхема КР580ВВ55А (старое обозначение К580ИК55А) - программируемое устройство ввода/вывода параллельной информации. Применяется в микропроцессорной технике в качестве элемента ввода/вывода общего назначения для подключения интерфейсных устройств (клавиатуры, принтера, накопителя на магнитной ленте и т. д.) к магистралям данных. Условное графическое изображение микросхемы показано на рисунке 7, а ее структурная схема - на рисунке 8. Данные о назначении выводов вы найдете в таблице 4.

|

|

|

| Графическое обозначение м/сх КР580ВВ55А | Структурная схема м/сх КР580ВВ55А |

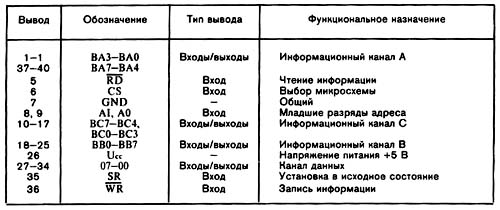

Таблица 4

|

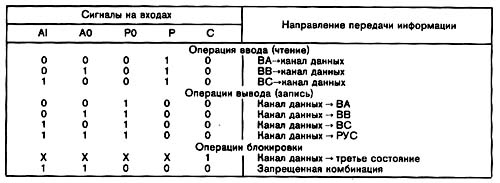

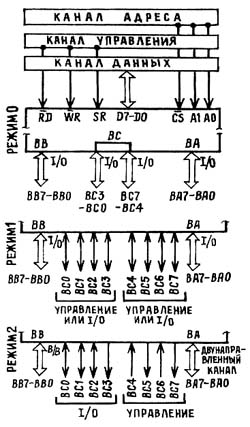

Обмен информацией между магистралью данных системы и микросхемой KР580BB55A осуществляется через 8-разрядный двунаправленный канал данных (D). Для связи с периферийными устройствами используются 24 линии ввода/вывода, сгруппированные в три 8-разрядных канала БА, ВВ и ВС, режимы работы которых и направление передачи информации определяются программным способом.

Микросхема имеет три режима работы. В режиме 0 обеспечивается синхронная, программно-управляемая передача данных через два независимых 8-разрядных канала ВА и ВВ и два 4-разрядных канала ВС.

В режиме 1 обеспечивается ввод или вывод информации "в" или "из" периферийного устройства через каналы ВА и ВВ по специальным сигналам. При этом линии канала С используются для приема и выдачи сигналов управления обменом информацией.

В режиме 2 обеспечивается возможность обмена информацией с периферийными устройствами через двунаправленный 8-разрядный канал ВА по специальным сигналам. Для передачи и приема сигналов управления обменом используются пять линий канала ВС. Выбор соответствующего канала и направление передачи информации через канал определяется сигналами А0, А1 (обычно соединяется с младшими разрядами канала адреса системы), RD, WR, CS в соответствии с таблицей 5.

Таблица 5

|

Режим работы каждого из каналов ВА, ВВ и ВС определяется содержимым регистра управляющего слова (РУС). Записав в него управляющее слово, микросхему можно перевести в один из трех режимов работы: режим 0 - простой ввод/вывод, режим 1 - стробируемый ввод/вывод, режим 2- двунаправленный канал.

При подаче сигнала SR регистр управляемого слова устанавливается в состояние, при котором все каналы настраиваются в режиме 0 для ввода информации. Режим работы каналов можно изменять не только в начале, но в самом процессе выполнения программы. Благодаря этому одна микросхема может в определенном порядке последовательно обслуживать несколько различных периферийных устройств. При изменении режима работы любого канала все входные и выходные регистры каналов и триггеры состояния сбрасываются. Разобраться в режимах работы каналов вам поможет рисунок 9.

|

Режимы работы каналов |

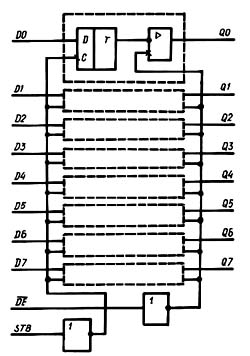

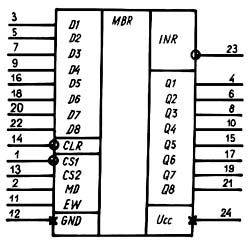

Микросхема К589ИР12 - многорежимный восьмиразрядный универсальный буферный регистр. На одной или нескольких микросхемах этого типа можно реализовать ряд интерфейсных и вспомогательных устройств: регистры данных, буферные регистры со стробированием данных, мультиплексоры, двунаправленные шинные формирователи, прерываемые каналы ввода/вывода и другие.

Условное графическое обозначение микросхемы показано на рисунке 10. Назначение выводов указано в таблице 6.

|

Графическое обозначение м/сх К589ИР12 |

Таблица 6

|

Микросхема состоит из восьми информационных триггеров, восьми выходных буферных устройств с тремя устойчивыми состояниями, отдельного D-триггера для формирования запроса на прерывания и гибкой схемы управления режимами работы регистра. Управляющие выводы микросхемы - CS1, CS2, MD и EW. Эти входы используются для управления выборкой устройств, информацией регистра, состоянием выходных буферных каскадов и триггером запроса на прерывание.

Вход MD (выбор режима) определяет один из двух режимов работы. При наличии на входе MD логического 0 устройство работает для ввода информации. В этом случае выходные буферные каскады открыты. Управление записью осуществляется сигналом по входу EW. При появлении на входе MD логической 1 устройство будет работать в режиме вывода. В этом случае выходные буферные каскады будут находиться в открытом состоянии независимо от выборки устройства, вход EW используется как синхросигнал для записи информации в регистр при наличии на входе MD логического 0 и для синхронной установки триггера запроса прерывания.

Триггер запроса прерывания служит для выработки соответствующего сигнала в микропроцессорной системе. При установке системы в исходное состояние низким уровнем сигнала CLR триггер запроса устанавливается в состояние запрета прерывания. Этот же сигнал заведует и разрешением прерывания. Считается, что микросхема находится в состоянии прерывания, когда на выходе INR устанавливается логический 0.

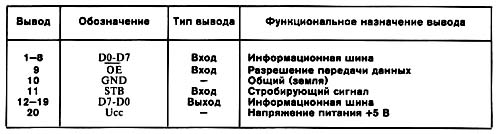

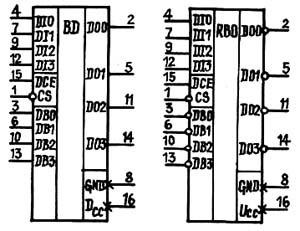

Микросхемы К589АП16 и К589АП26 - двунаправленные шинные формирователи, своего рода усилители цифровых сигналов. Отличаются они тем, что, проходя через микросхему К589АП16, сигнал остается неизменным, а через К589АП26 - инвертируется. Используются эти микросхемы для управления шинами (магистралями) в цифровой и микропроцессорной технике. Обе микросхемы представляют собой 4-канальные коммутаторы, имеющие в каждом канале одну шину только для приема информации и одну двунаправленную шину для приема и выдачи информации.

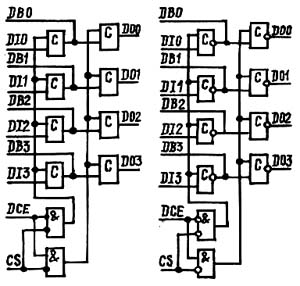

Условное графическое обозначение микросхем показано на рисунке 11, а структурная схема - на рисунке 12. Назначение выводов указано в таблице 7.

|

|

|

| Графическое обозначение м/сх К589АП16 и К589АП26 | Структурная схема м/сх К589АП16 и К589АП26 |

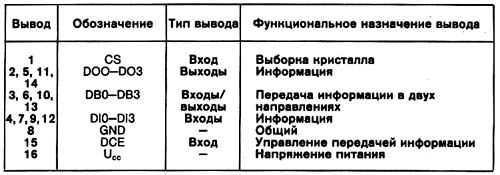

Таблица 7

|

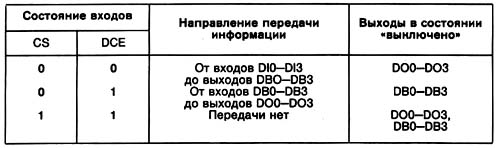

Для управления режимами работы и направлением выдачи информации используется специальная схема на двух элементах 2И. При появлении на входе CS подается логическая 1, формирователи переходят в выключенное высокоомное состояние. При наличии на входе CS логического 0 управление выдачей информации по шинам D0 и DВ осуществляется сигналом на входе управления выдачей информации DСЕ. Если на входе DCE логический 0, то открыта передача информации со входов DI на выходы DВ. При сигнале с уровнем логической 1 на этом же входе происходит передача информации с входов DВ на выходы 0 (см. таблицу 8).

Таблица 8

|